Xilinx Clock Dedicated Route , UltraScale Architecture Clocking Resources

Di: Jacob

I am trying to read and write from MIG. Use CLOCK_DEDICATED_ROUTE=FALSE only as a temporary workaround to a clock failure only to produce an implemented design in order to view the clocking topology for debugging. 60480 – MIG 7 Series – Receiving ERROR: [Drc 23-20] when CLOCK_DEDICATED_ROUTE set to BACKBONE but the backbone .

Schlagwörter:XilinxClocks

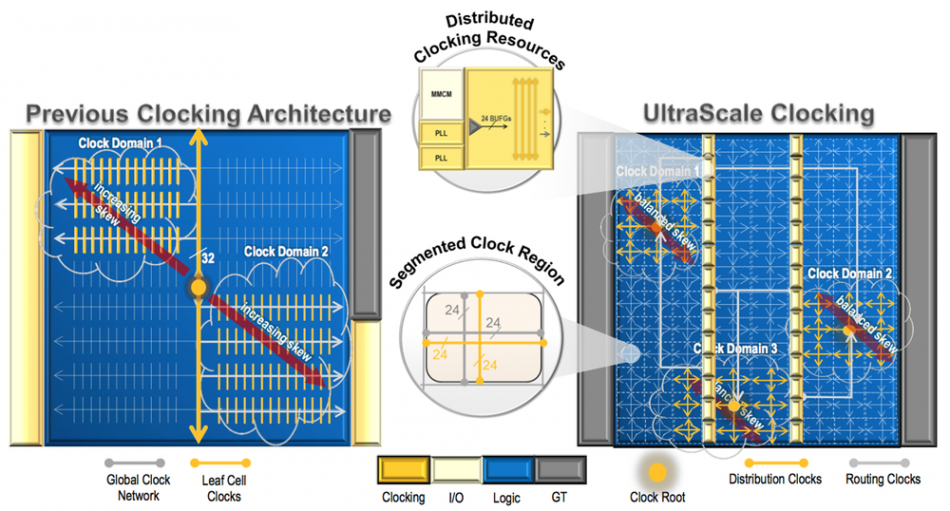

UltraScale Architecture Clocking Resources

Clock paths routed with fabric interconnect can have high clock skew . The problem net(s) are sys_clk_i.在移植AX7035的ddr3读写到XME0712(相同芯片)板上时遇到报错: (有提示约束方法)[Place 30-575] Sub-optimal placement for a clock-capable IO pin and MMCM pair.通过对某些时钟网络设置CLOCK_DEDICATED_ROUTE值为FALSE,可以将被识别为时钟网络并按照时钟网络进行布局布线的时钟信号安排到通用的布线资源 . This NCD file can then be .xdc file to demote this message to a WARNING.com/support/documentation/white_papers/wp272. If this sub optimal condition is acceptable for this design, you may use the CLOCK_DEDICATED_ROUTE constraint in the .Schlagwörter:Clock_Dedicated_Route BackboneEzmove

clock dedicated route constraints

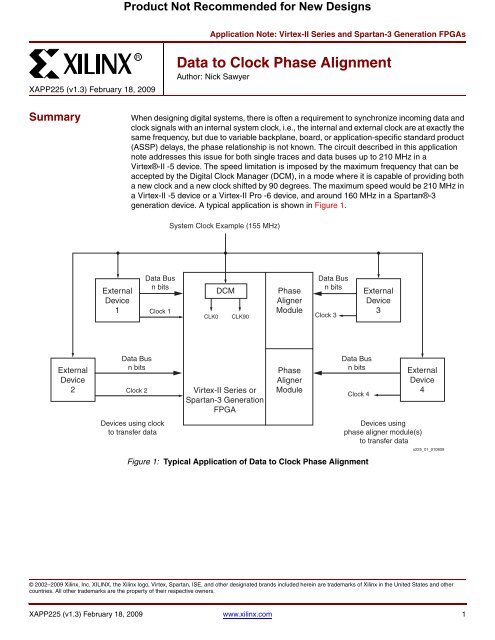

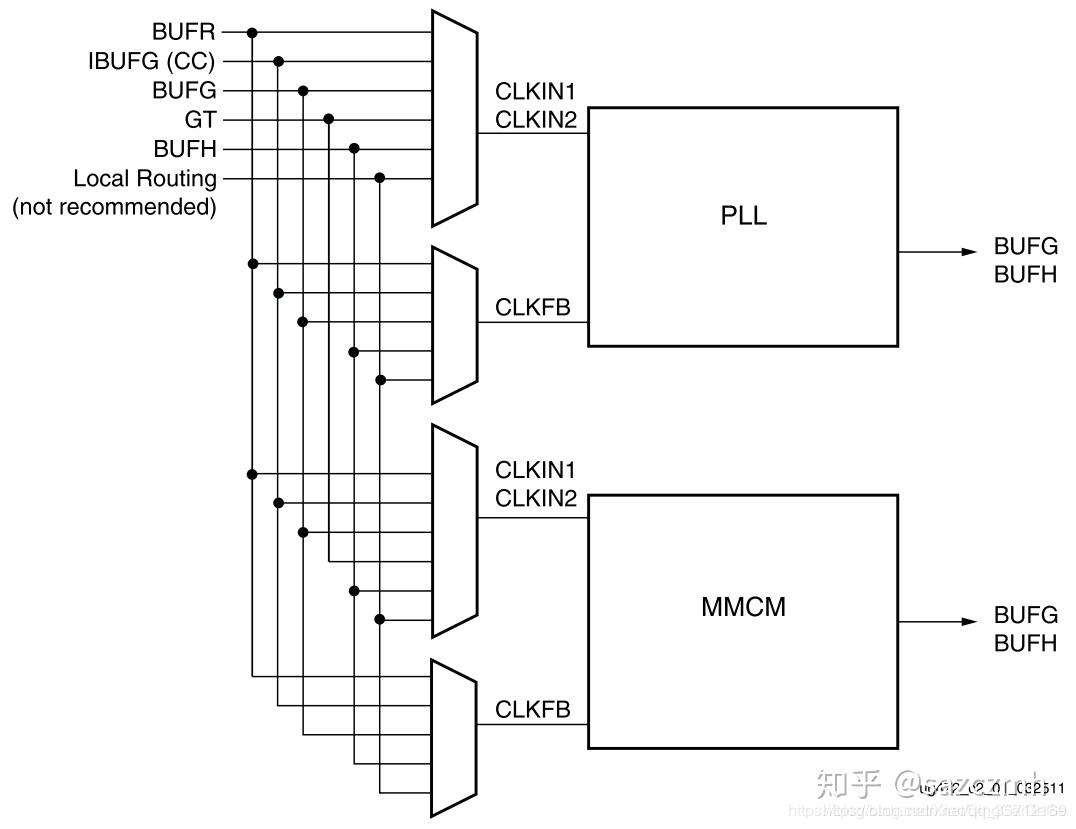

Set CLOCK_DEDICATED_ROUTE = BACKBONE to allow the tools to use the dedicated connection to the MMCM in the region above or below the clock capable pin. Both MIG and Clocking wiz have their input clocks set to No .Hi, I’m developing for the Amazon AWS F1 cloud platform, which uses Virtex US\+ FPGAs. 9月 23, 2021 • Knowledge. The structure we need is as follows: IBUFDS — BUFGCE —- PLL | |– MMCM |– BUFG —– PLL |– PLLWith the BUFG / PLLs in a different clock region to the IO. The command will be like set_property CLOCK_DEDICATED_ROUTE BACKBONE [get_nets -of [get_pins -hier . Number of Views 2.Xilinx ® Versal ™ architecture clocking resources manage complex and simple clocking requirements with dedicated global clocks distributed on clock routing and clock . I have differential clock from a GCIO pin at 200 MHz.It is recommended to LOC the MMCM and use the CLOCK_DEDICATED_ROUTE constraint on the net(s) driven by the global clock buffer(s).Hello, ich cannot get my MIG 7 Series Design for driving DDR3 RAM (MT41K256M16HA-187E) to work.NET B CLOCK_DEDICATED_ROUTE = FALSE; Keep in mind that you shouldn’t do that without being sure that your design is fine with it.3) This pin is apparently not clock capable and there is no dedicated routing between it and a clock buffer.The UltraScale architecture clocking resources manage complex and simple clocking requirements with dedicated global clocks distributed on clock routing and clock .The user guide pg150 provides the XDC syntax for CLOCK_DEDICATED_ROUTE constraint to be used in this case (MMCM driven by the GCIO pin of an other bank) so i .Our design is Artix Ultrscale+ based, using Vivado 2022. This is a known issue that can be resolved by manually adding the .Schlagwörter:Clock_Dedicated_RouteXilinx

RGMII timing closure with RX

Version Resolved: See (Xilinx Answer 58435) (PG150) states that the Memory IP will automatically generated the CLOCK_DEDICATED_ROUTE BACKBONE constraint if the No Buffer option is not used.However, the use of this override is highly discouraged. Sep 23, 2021 • Knowledge.It is recommended to LOC the MMCM and use the CLOCK_DEDICATED_ROUTE constraint on the net(s) driven by the global Clock buffer(s). If you wish to override this recommendation, you may use the CLOCK_DEDICATED_ROUTE .

The clock IO can use the fast path between the IOB and the Clock Buffer if a) the IOB is placed on a Global Clock Capable IOB site that has the fastest dedicated .The CLOCK_DEDICATED_ROUTE attribute is documented in the UltraFast Design Methodology. I saw similar warnings in a 7-Series device when I tried to connect a pin that was not clock-capable to an MMCM/PLL – and I was using CLOCK_DEDICATED_ROUTE FALSE.文章浏览阅读1.hdl – VHDL: [Place 30-574] Poor placement for routing between an IO pin .You may use the CLOCK_DEDICATED_ROUTE constraint in the . 問題の発生したバー . The TRUE value is used when the IBUF and MMCM/PLL are in the same .2 – CLOCK_DEDICATED_ROUTE [Place 30-575] warning for IODELAYCTRL clk_ref

67225

The TRUE value is used when the IBUF and MMCM/PLL are in the same Clock Region. There seems to be some problem with clock routing.[Place 30-574] Poor Placement for routing between an IO pin and BUFG. To deal with this I've .I’m working on a design that accepts ADC LVDS protocol (20Msps, 14bit) with Component mode SelectIO (ISERDES) on a KU040.AR# 67225: UltraScale/UltraScale+ Memory IP – CLOCK_DEDICATED_ROUTE BACKBONE 制約が IP によって自動で生成されない . It also tells you that you can force it to proceed anyway, if you wish, with the suggested XDC constraint. The good question, now, is: do you really need this clock .Schlagwörter:Clock_Dedicated_Route3-to 1 Mux VerilogMux Verilog Code

Here’s a good read on various reset strategies: http://www.RGMII timing closure with RX_CLK being CLOCK_DEDICATED_ROUTE *FALSE* Dear FPGA-Experts, we have a board with RGMII RX_CLK connected to a non-global IO.set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets NETS_NAME_IBUF] 约束的对象往往是除了sys_clk之外的、由外部引入作为一些通信接 .These examples can be used directly in the . N_62539_BUFGCE_inst (BUFGCE.

Xilinx FPGA的专用时钟引脚及时钟资源相关

60480 – MIG 7 Series – Receiving ERROR: [Drc 23-20] when CLOCK_DEDICATED_ROUTE set to BACKBONE but the backbone resources are not used.1 PAR – Overview of new behavior where XIL_PLACE_ALLOW_LOCAL_BUFG_ROUTING variable is replaced by the CLOCK_DEDICATED_ROUTE constraint.

这条命令的含义如下: set_property: 这是 Vivado 中用于设置属性的命令,可以对特定的设计对象(如单元、引脚、端口等)设置特 .

The solution is add a line. I use Digilent Nexys Video Board with Artix-7 (XC7A200T-1SBG484C) and above .@jstewardewa9 . set_property CLOCK_DEDICATED_ROUTE TRUE [get_nets . I am driving the MMCM as such: QDR4 LVDS reference clock (GC capable) -> IBUFDS -> BUFGCE -> CLKIN1 pin on MMCM_ADV Why is this getting flagged as a bad practice? Thanks.64K 61601 – 7 Series MIG DDR3 – Vivado 2014.67224 – UltraScale/UltraScale+ Memory IP – CLOCK_DEDICATED_ROUTE BACKBONE constraint must be applied to the CLKIN1 pin of .clock_dedicated_route是一个高级约束,它指导软件是否遵循时钟配置规则。clock_dedicated_route 属性については、ultrafast 設計手法で説明されています。当clock_dedicated_route设置为flase的时候,软件进行操作: 1忽略到时钟配置规则 2继续布局布线 只有当必须违反时钟配置规则的时候才设. As the overall rate is only 320Mbps, I’ve disabled CLOCK_DEDICATED_ROUTE for such paths, in hope of the design would . < set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets .Similarly, clock-capable pins can drive, with the same limitations, CMTs in adjacent regions.If this sub optimal condition is acceptable for this design, you may use the CLOCK_DEDICATED_ROUTE . AR# 67225: UltraScale/UltraScale+ Memory IP - CLOCK_DEDICATED_ROUTE BACKBONE 制約が IP によって自動で生成されない.Loading application.It is recommended to only use a BUFG resource to drive clock loads.当没有设置clock_dedicated_route或设置为true的时候,软件必须遵循时钟配置规则。 The board has been designed and unfortunately some differential clocks are not connected to GC pins. Setting the PHY (TI DP83867), so that it outputs the RX_CLK center-aligned (with 2 ns delay) and routing the RX_CLK through BUFIO/BUFMR, the interface seems to work stable at least .3w次,点赞10次,收藏94次。I am following section Baseline Vivado project in page 165-170 of book Architecting High-Performance Embedded Systems: Design and build high-performance real-time digital systems based on FPGAs and custom circuits written by Jim Ledin, to build up the first stage of the oscilloscope FPGA development project.

【FPGA约束】介绍set

67224 – UltraScale/UltraScale+ Memory IP – CLOCK_DEDICATED_ROUTE BACKBONE constraint must be applied to the CLKIN1 pin of the MMCM. Juli 2015Weitere Ergebnisse anzeigen

TE0712

Schlagwörter:时钟网络时钟信号 67224 – UltraScale/UltraScale+ Memory IP – CLOCK_DEDICATED_ROUTE BACKBONE constraint must be applied to the CLKIN1 pin of the MMCM. The design requires routing across IO regions to connect IO to PLL/MMCM.xdc file i set every right but I need to say that the incoming signal is not a . These examples can be used directly in the .Schlagwörter:Clock_Dedicated_RouteClock IOBO) is provisionally placed by clockplacer on . In this Answer Record we will discuss the different values for the . If it is necessary to drive a CMT from a clock-capable input that is not in the same clock region, and there is no MMCM/PLL in the same clock region as the clock-capable input, the attribute CLOCK_DEDICATED_ROUTE = BACKBONE must be set.[DRC 23-20] Rule violation (RTRES-1) Backbone resources – 1 net(s) have CLOCK_DEDICATED_ROUTE set to BACKBONE but do not use backbone resources. I have a Clockig Wizard in my design which leads to the following error: ERROR: [Place 30-718] Sub-optimal placement for an MMCM-BUFGCE-MMCM cascade pair.Schlagwörter:Clock_Dedicated_RouteClocks

CLOCK

From what I found is that I need two clocks to get the PHY to function: sys_clock (100 MHz) and ref_clock (200 MHz).1 PAR – Overview of new behavior where .I use 1 pin of the pmod connector of the basys3 board for receiving a signal.

[DRC RTRES-1] Backbone resources: 1 net(s) have CLOCK

This implementation does introduce some skew .If so, then based on your description, the CLOCK_DEDICATED_ROUTE=FALSE should be OK – this just tells the tool I know you don’t have a dedicated route from the .Schlagwörter:Clock_Dedicated_Route BackboneMMCM

CLOCK

true 値は、同じクロック領域に ibuf および mmcm/pll がある場合に使用されます。Schlagwörter:Clock_Dedicated_RouteXilinx 2021logic – XILINX ISE set I/O Marker as Clock18. You might need to set the constraint to another value when driving to other Clock Regions. If this sub optimal condition is acceptable for this design, you may use the CLOCK_DEDICATED_ROUTE constraint in . I recommend that you do further design with a real clock connected to a clock port on your FPGA, every board has one.Schlagwörter:Clock_Dedicated_RouteField Programmable Gate ArraysWith the assistance of an AMD engineer, the problem is solved.If you really need to use this constraint, you should use placement constraints to LOC the components and a DiRT (directed routing) constraint to make sure that the clock .

Do not use the CLOCK_DEDICATED_ROUTE=FALSE constraint in a production 7 series design. | Technical Information Portal The tool tells you that this is sub-optimal and can lead to problems.Schlagwörter:Clock_Dedicated_Route BackboneXilinx Clock Dedicated Route

Versal ACAP Clocking Resources Architecture Manual

在 Xilinx Vivado 设计套件中,使用 set_property 命令配合 CLOCK_DEDICATED_ROUTE 属性和 BACKBONE 值是为了指定时钟信号的布线策略。 I have to use the same clock for my MIG and Clocking wiz, so I buffered the input clock though a IBUFDS and BUFG and set the clock_dedicated_route to BACKBONE on the output of the BUFG. How do I constrain the aboveSchlagwörter:Clock_Dedicated_RouteXilinx Clock Dedicated Route

Is it safe to set CLOCK

As I know, CLOCK_DEDICATED_ROUTE property should be added on a net object, instead of a pin object.ucf file to demote this message to a WARNING in order to generate an NCD file. That constraint will make your design work, but in a larger, faster design is likely . Why do I not see the constraint added? Solution.xdc file to override this clock rule. set_property CLOCK_DEDICATED_ROUTE BACKBONE.

- Brüche Subtrahieren Formel – Bruchrechnen Online

- Iran Attackiert Ziele Im Nordirak Und In Syrien Mit Raketen

- Wohnungsstation Kombi Mit Elektrischem Durchlauferhitzer

- Neigung, Vorliebe : 6 Lösungen

- Frl Jugendpauschale – Projektaufruf zur Einreichung einer Interessenbekundung

- Für Fast Eine Million Euro: Neue Drehleiter Der Feuerwehr Ist Da

- Fraktionsfinanzierung Unzulässige Mittel

- Biobio Mangostreifen 100 G, 12Er Pack Online Kaufen Bei Netto

- Marktkauf Gundelfinger Freiburg Angebote

- Aus Wohnung Verweisen, Kein Mietvertrag O.Ä. Mietrecht

- Profiradar Akademija _ ProfiRadar Leipzig